半導体業界の”プロセス(7nmとか)”をできるだけ理解する

7nm、4nm、3nm、…。この寸法の表現をプロセス名などと呼ぶそうで、なんとなく”小さいほど微細そうで技術が進んでいる”といった印象を受けます。ただ、これが何の長さを表しているのか、業界全体の規格で定められているのか、等、色々と気になりました。

本記事は、そのあたりのことを調べた際のメモです。

本記事の目的

- 半導体業界の”プロセス”をできるだけ理解する。

本記事における用語と詳細さ

本記事では、半導体業界で使用されるプロセスの呼称のことを”プロセス名”と記載します。

プロセス、プロセスノード、ノード、technology node(IRDS)といった表現については、同じ意味として扱います。

また、MPU、ASIC、DRAM、NAND等の構造の違い等は細かく区別していません。

その他の用語についての説明は、別記事にまとめる予定です(いつか)。

プロセス名の変遷

当初のプロセス名

半導体技術に関する国際的なロードマップであるIRDSの資料に記載されている経緯は以下のようなものです。

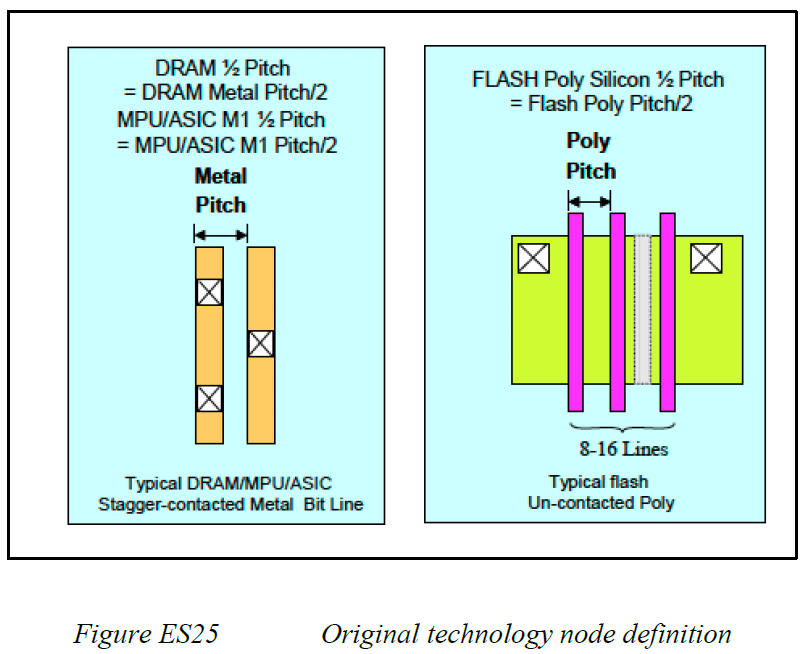

1992年から、NTRS、ITRS、そしてIRDSといったロードマップ活動により、プロセスに対する命名方法が提示されてきました。

それにより、当初はプロセス名として以下のいずれかが用いられました。

- 集積回路の中で最も密度の高い金属レイヤの配線ピッチの1/2

- トランジスタのゲートの長さ

1970年代~1990年代の途中までは、上記の、配線ピッチの1/2と、ゲートの長さは本質的に同一である、という前提がありました。

そのため、このプロセス名という1つの数値により、密度の概念と、パフォーマンスの概念の両方を表すことができました。

- 密度の概念:配線ピッチの1/2が小さいほどトランジスタ密度は高くなるという相関性

- パフォーマンスの概念:ゲート長が短いほどトランジスタは高速という相関性

上記より、プロセス名は半導体技術の進歩の度合いを示す際に、客観的で便利な尺度だったように思われます。

その後~現在のプロセス名

引き続き、IRDSの資料を参照します。

90年代後半から、PCの普及によりプロセッサ技術がより発展します。

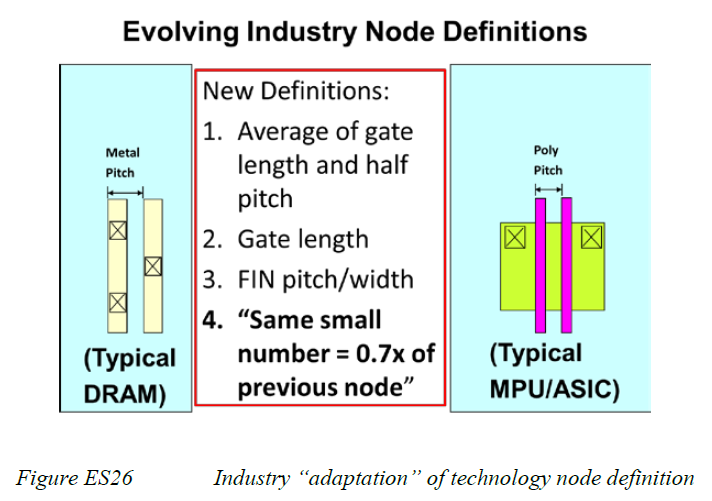

その競争の際、半導体業界の各社によりプロセス名の定義が変化していったようです。

-

ゲートの長さと、配線ピッチの1/2の平均

-

ゲートの長さ

-

フィンのピッチもしくは幅

-

(最終的に)前世代のプロセス名が何であれ、それに用いられている長さの70%

前世代の70%の長さがプロセス名

IRDSからの引用です。

Finally, the technology node definition became 70% of whatever the name of the node of the previous generation was! (See Figure ES26.)

IRDS 2022 Edition Executive Summary “1.2.2. BRINGING THE NODE NOMENCLATURE BACK TO NORMAL”より

文末の”!”が印象的です。

とにかく、前世代のプロセス名の70%程度の長さが、その次の世代のプロセス名として用いられるようになったということです。

例えば、Intelの3世代分のプロセス名、Intel 7(7nm) → Intel 4(4~5nm) → Intel 3(3nm)は、確かにだいたい0.7倍で推移しています。

この70%という割合とムーアの法則の関連性についての補足は、後述します。

ではプロセス名の長さに意味はあるのか

この命名方法により、集積回路のスペックとプロセス名は、関係が無くなりました。

実際、”7nm”のプロセスと言っても、半導体ウエハー上で7nmの長さで加工される部分は無いようです。

つまり、半導体業者の各社が自社の技術や製品をアピールし、ロードマップやその実績を示すために用いる表現ということになります。

そのため、IRDSではプロセス名に用いられる寸法のことを”industry labeling”とも説明しています。

素人目にはやはり、なんとなく”小さいほど微細そうで技術が進んでいる”といった印象を受けるということになります。

IRDSにおけるプロセスの定義

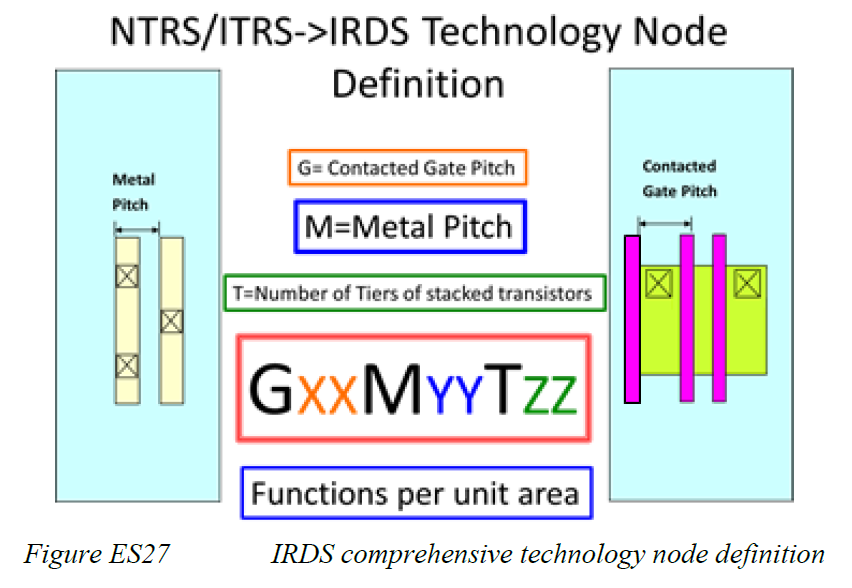

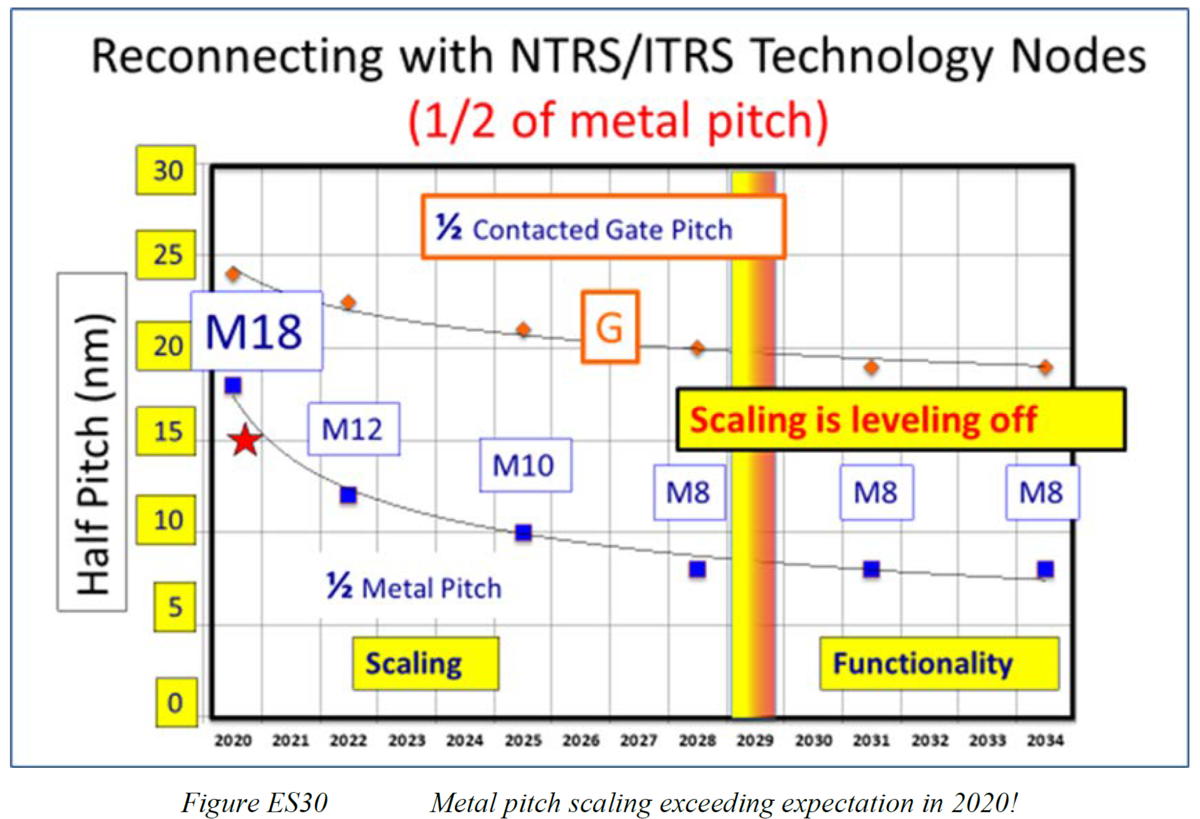

IRDSでは、NTRSやITRSの定義を引き継ぎつつ、プロセスの定義方法が提示されています。

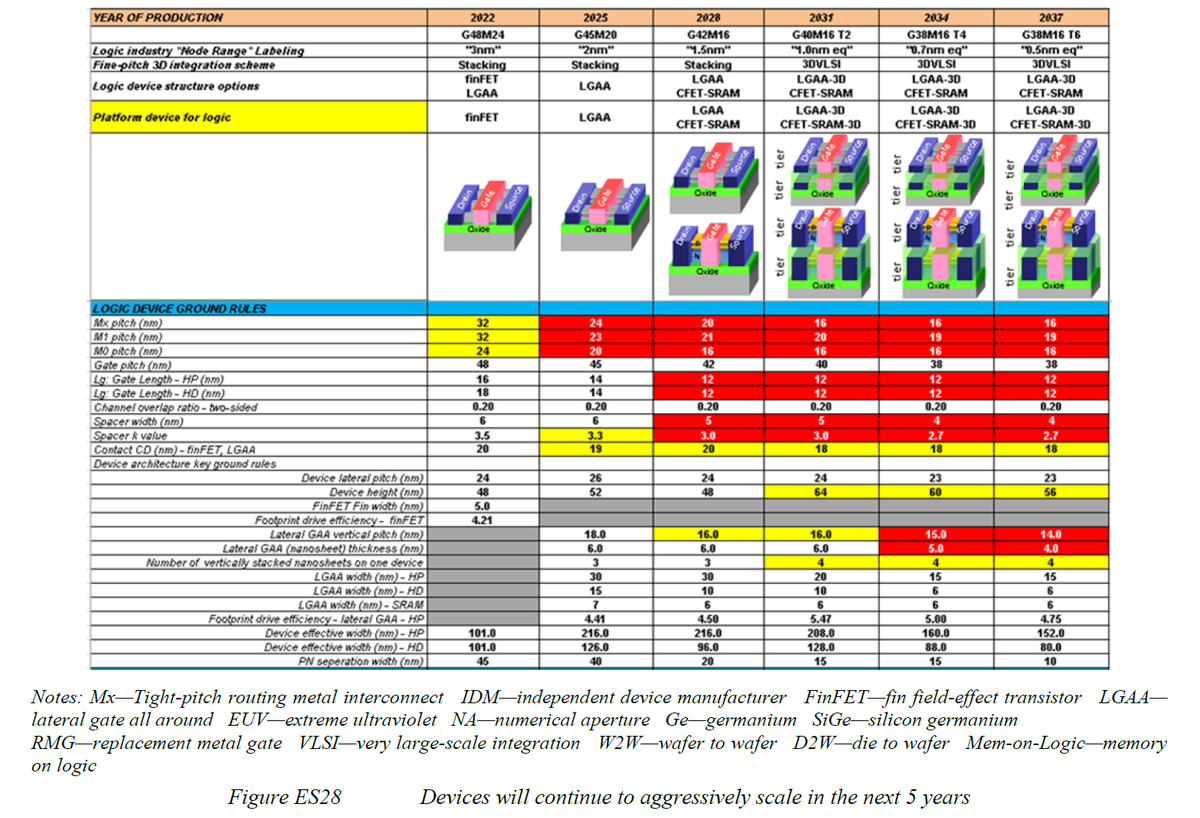

IRDSは15年先までのロードマップなので、表は2022年、3nmプロセスから始まっています。

表の2行目が主要なノード属性ということで、Gがcontacted gated pitch(CGP、接触ゲートピッチもしくはCPP(接触ポリピッチ))、Mがtightest metal pitch(MP、金属レイヤの最小配線ピッチ)を表しています。

“プロセス名”そのものの定義はありませんが、世代ごとのプロセスの構造や属性が分類されています。

表の3行目のLogic industry “Node Range” Labelingの箇所が、前述のように半導体業界で用いられる”industry labeling”に相当するものと思われます。

なお、この定義方法に強制力は無いので、各社が従っているわけではありません。

今後のMP、CGPのスケール

金属レイヤの最小配線ピッチ(MP)は7~8nmが限界(fundamental limit)とのことで、今後10年間でその水準に達するという予測のようです。

各社のプロセス名のばらつき

上記の経緯により、半導体業界の各社は、自社の製品や技術を説明する際、集積回路のスペックと直接関係のない長さに由来するプロセス名を使用するようになりました。

結果、そのプロセス名が主張する長さが同じであっても、実際の集積回路の加工寸法にはバラつきが生じる場合があります。

例えば、下図のようにIntelの10nmプロセスはTSMCの7nmプロセスと同等、Intelの7nmプロセスはTSMCやSamsungの5nmプロセスと同等、といったバラつきです。プロセス名だけを見ると、Intelが他社より1世代遅れているように見えます。

その後、Intelは2021年にプロセス名の呼称を変更済みです。

“Enhanced 10nm SuperFin”を”Intel 7″に変更(10nm→7nmに修正)、その後の世代は、Intel 4(4~5nm)、Intel 3(3nm)、Intel 20A(2nm)です。

TSMCでは、N7(7nm)、N5(5nm)、N3(3nm)といったプロセスの呼び方です。

プロセスと関連するもの

前世代の70%とムーアの法則

前世代のプロセス名の70%程度の長さ、というのは、ムーアの法則が示すレートに近い目安でもあります。

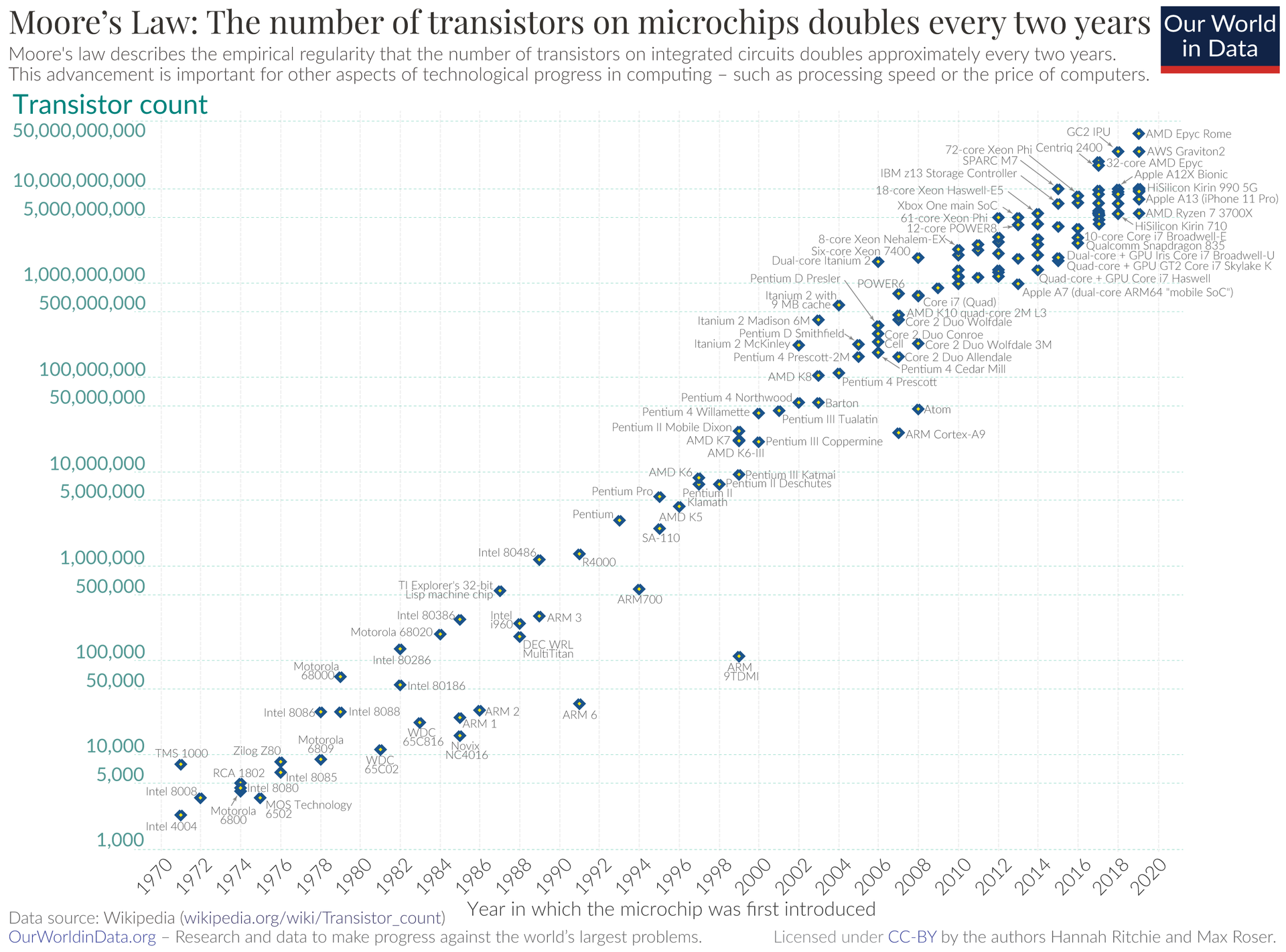

ムーアの法則は、インテル社の創業者の1人、ゴードン・ムーアが示したもので、集積回路の中のトランジスタ数が約2年で2倍になるという予測です(当初1965年に示され、その後、1975年に修正された結果、”1980年頃まで毎年2倍、その後は約2年で2倍”と予測)。

2年後に2倍、4年後には4倍、6年後には8倍、8年後には16倍のように、指数関数的な増加トレンドを示すものです。

プロセス名の由来と関連のある集積回路の最小加工寸法が0.7倍になるということは、面積にすると 0.7 × 0.7 = 0.49 ≒ 0.5 となります。これにより、単純化すると同じ数のものを半分の面積に収められる(面積が同じなら2倍の数のものを収められる)という考え方はできます。新世代のプロセスを2年ごとに導入すれば、”2年で2倍”ということになります。

ただ実際の集積回路は世代とともに構造自体も変化していることもあり、物理的に何を表すのかが曖昧な長さや、それを基に計算した面積だけでは集積回路に収められるトランジスタ数を表すことは難しいため、ムーアの法則と一致している訳ではありません。微細さのスケール表現のおおまかな対応づけになる程度でしょう。

なお、プロセス名でなく半導体業界の技術自体は、このムーアの法則と同等のペースで進歩してきましたが、近年では、技術的、物理的な課題によりムーアの法則を維持することは難しいとも言われています。

あと補足として、2倍になる期間を2年でなく18か月であるとする指標は、トランジスタ数でなく、消費電力あたりのチップ性能が2倍になる期間を18か月であると予測した David House によるものです。これは、ムーアの法則とは異なります。

ゲート長と論理回路の性能

IRDS 2022では、あわせて以下の点についても記載されています。

-

ゲート長を小さくすることは、もはや論理回路の性能に支配的な影響を与えない

-

トランジスタの速度より、消費電力を削減することが重要

- ウエハーの冷却が不要になる120~130Wの電力に収める

詳細は、トランジスタ構造や論理回路の性能に関する話になると思います。

まとめ

半導体業界の”プロセス”について調べた結果をまとめてみました。

専門的なのできちんと理解するのは難しいのですが、技術が進歩し続けている雰囲気を感じることはできます。